SIGARCH

This article is the first in a two-part series that summarizes the key contributions of 4th Data Prefetching Championship (DPC-4), held in conjunction with the 32nd iteration of HPCA in 2026. While discussing innovative data prefetching techniques presented in this contest, we focus on the functionality of proposed algorithms and also explain why they are […]

Hybrid continuous-discrete-variable (CV-DV) quantum computing combines oscillators and qubits to tackle problems that are difficult for either model alone, from bosonic simulation to quantum error correction. At ASPLOS 2026, our tutorial introduced the foundations, compilation stack, benchmarking methods, and programming tools behind this emerging architecture model. In this blog post, we overvie…

For decades, we have designed chips in fundamentally the same way: human intuition applied to a vanishingly small slice of an impossibly large design space. That paradigm worked when Moore’s Law was lifting everything. We could afford to be wrong. We could afford to miss the best design. Process scaling would close the gap. That […]

Years ago, I came across three pioneering works (CSI-NN, Cache Telepathy, and DeepSniffer) in the field of reverse engineering neural networks that inspired my journey into side-channel attacks to uncover the secrets of modern Deep Neural Networks (DNNs). Fast forward to today, and there has been significant exploitation of side-channel attacks to discover the secrets of neural networks. It’s a g…

Call for Participation: Greater Chicago Area Systems Research Workshop (GCASR) 2026 https://gcasr.org/2026 Submitted by Peter Dinda 13th Greater Chicago Area Systems Research Workshop (GCASR 2026) May 11, 2026 Northwestern University, Evanston, Illinois https://gcasr.org/2026 The GCASR Workshop, now in its 13th iteration, is a premier venue that promotes awareness, collaboration, and synergy amon…

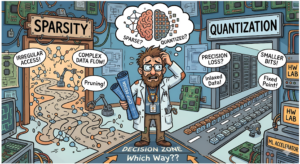

The debate of sparsity versus quantization has made its rounds in the ML optimization community for many years. Now, with the Generative AI revolution, the debate is intensifying. While these might both seem like simple mathematical approximations to an AI researcher, for a hardware architect, they present fundamentally different sets of challenges. Many architects in the AI hardware space are de…

As we close the book on 2025, Computer Architecture Today has seen another successful year of community engagement. We published 29 posts covering a wide spectrum of topics—from datacenter energy-efficiency to the evolving debate on LLMs in peer review, alongside trip reports from our major conferences. I want to thank all our authors for their insights, with special appreciation for those who co…

Large language model (LLM) agents are quickly moving from “single agent” to *multi-agent systems*: tool-using agents, planner-orchestrator, debate teams, specialized sub-agents that collaborate to solve tasks. At the same time, the *context* these agents must operate within is becoming more complex: longer histories, multiple modalities, structured traces, and customized environments. This combin…

TL;DR: Latency-tolerant architectures, e.g., GPUs, increasingly use memory/storage hierarchies, e.g., for KV Caches to speed Large-Language Model AI inference. To aid codesign of such workloads and architectures, we develop the simple PipeOrgan analytic model for bandwidth-bound workloads running on memory/storage hierarchies. Background For three reasons, memory bandwidth, more than latency, lim…

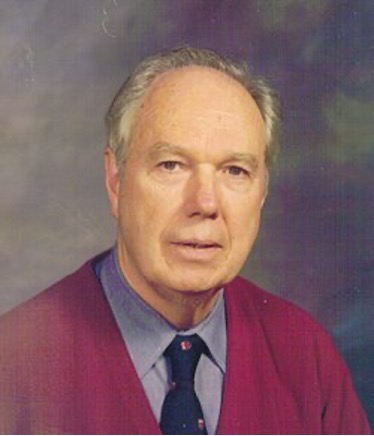

Michael J. Flynn is a widely respected contributor—indeed a giant—in the field of Computer Architecture. He made highly significant and impactful contributions throughout his career, both in industry and in academia. Sadly, he passed away peacefully December 24, 2025, having lived a long and full life. Born May 20, 1934, in New York, NY, Flynn earned his Bachelor’s, Master’s, and Ph.D. degrees in…

Microarchitecture simulators have been conceived and implemented to be valuable tools for the design of computing chips of all types (SimpleScalar, gem5, SMTSIM, Sniper, Qflex, Scarab, GPGPU-sim, Accel-Sim, Multi2Sim, NaviSim, SCALE-sim, gem5-Salam, TAO, PyTorchSim – the list is neither historically complete nor updated). In essence, microarchitecture simulators have an “impossible” objective: to…

This is the second article in the series, following our first blog in Dec 2023: https://www.sigarch.org/tuning-the-symphony-of-heterogeneous-memory-systems/ Modern applications are increasingly memory hungry. Applications like Large-Language Models (LLM), in-memory databases, and data analytics platforms often demand more memory bandwidth and capacity than what a standard server CPU can provide. …

CAL has held a unique place in the computer architecture community for well over two decades as a periodical for publishing early and exciting results. CAL papers are only four pages long and undergo rigorous peer review to select those with novel ideas and/or insights that are of interest to the computer architecture community and may have high impact. Another unique attribute of CAL is that it …

A little while ago, I published a post on this blog titled, “The Reviewer is Dead, Long Live the Review: Re-engineering Peer Review for the Age of AI.” In it, I argued that the traditional human-only peer-review system is buckling under the weight of rising submission volumes, reviewer fatigue, and misaligned incentives. I proposed that modern LLMs have reached a point of technical sophistication…

This post is a much simplified introductory chapter of an open, online textbook, Foundations of Visual Computing. Visual computing is wonderfully broad, touching everything from the sciences of human vision to the engineering of sensors, optics, displays, and computer systems. While each of these areas is well covered in excellent texts, they are rarely explored […]

Matrix multiplication dominates AI hardware and research. Betting everything on MatMul risks an innovation monoculture — it’s time to diversify our compute bets.

Since publishing my piece on prioritizing energy accounting in data centers back in June, there’s been a steady wave of media coverage highlighting the rapid growth of datacenters and their impact on energy demand. On August 17, The Economist reported that U.S. household electricity costs have risen by 7% in 2025, partly due to the […]

The 7th annual Undergraduate Architecture Mentoring (uArch) Workshop took place alongside the International Symposium of Computer Architecture (ISCA) 2025, in the vibrant city of Tokyo, Japan! Similar to previous years, uArch was conducted in a hybrid format, combining in-person and virtual elements.The workshop introduces undergraduate and early master’s students to research and career paths in …

I am a COMPUTER ARCHITECT, which means I design computers. I was trained at a great school (UW-Madison), and I worked in industry (Intel) before I became a professor (University of Michigan). Despite these rarefied experiences, I first came to know computer architecture in the KITCHEN, working for 4 years as a COOK. Let me […]

research.io

research.ioSign up to keep scrolling

Create your feed subscriptions, save articles, keep scrolling.