Semiconductor Engineering

AI power prediction; large-area FPCBs; graphene vibrations. The post Research Bits: May 5 appeared first on Semiconductor Engineering .

Long‑running agents, tool-calling LLMs, and multimodal chaos are rewriting edge compute rules, and making chip design more challenging. The post Designing Chips In The Context Of Rapidly Evolving AI appeared first on Semiconductor Engineering .

Reasoning in semiconductor design. The post From Simulation Checkpoints To Continuous Physics appeared first on Semiconductor Engineering .

A new technical paper, “Nonvolatile photonic field-programmable coupler array,” was published by researchers at University of Oxford. Abstract “Programmable photonic networks carry out universal unitary functions by independently operating on the amplitude and phase of guided light. Exploiting the reconfigurability and spatiospectral degrees of freedom of these systems, the majority of state-of-t…

Google's TPUs now for sale; 2/3nm capacity crunch; IC tool sales to China stopped; memory shortage widens in 2027; mega-earnings; Arm's agentic toolkit; Intel seeds universities; KAIST's liquid cooling for advanced packages; MIT-IBM tool for estimating power; V2X collaboration. The post Chip Industry Week in Review appeared first on Semiconductor Engineering .

Turning billions of violations into actionable insights. The post Transforming DRC Closure At Advanced Nodes appeared first on Semiconductor Engineering .

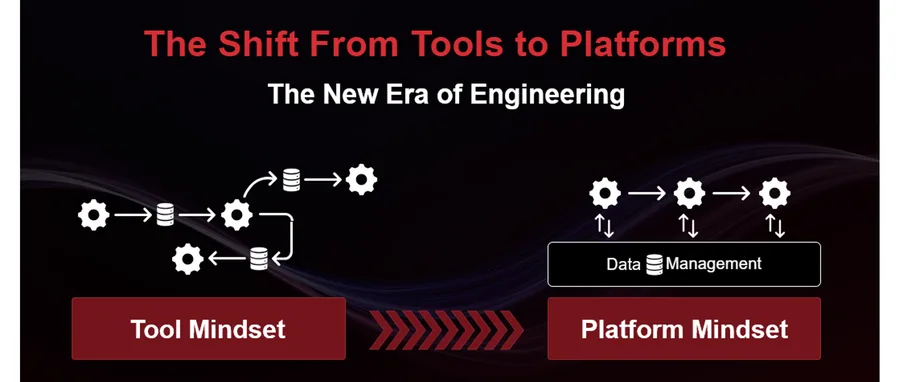

Current approaches involve multiple tools, vendors, designs, data formats, and abstractions. Can agents really use them all? The post Creating Agentic EDA Methodologies appeared first on Semiconductor Engineering .

The inability to access leading-edge process nodes has created opportunities for small and midsize chip developers in multi-die design, but it requires some sophisticated architectural design tradeoffs. The post Foundry Capacity Is Limiting Who Competes At Leading Edge Nodes appeared first on Semiconductor Engineering .

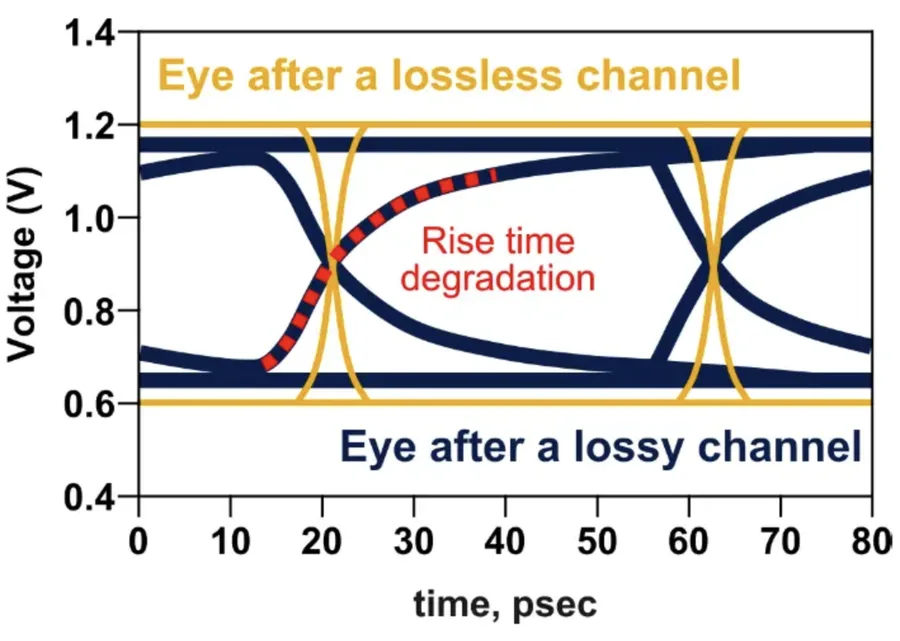

Analyze the effects on eye diagrams, BER, and timing margins by integrating advanced equalization algorithms into channel simulations. The post Unlocking High-Speed Serial Link Signal Integrity With AMI Model appeared first on Semiconductor Engineering .

The boundaries between IP reuse, interconnect design, and hardware-software integration are no longer independent. The post Facilitating Complex SoC Design Through Automation And Integration appeared first on Semiconductor Engineering .

Identifying and addressing design gaps in advanced packages. The post How To Streamline Your Advanced Package Interconnect Designs appeared first on Semiconductor Engineering .

Traditional simulations lack an understanding of clocking requirements and cannot handle the complete clock network of a large chip. The post Solving Clock Signal Integrity And Jitter Issues appeared first on Semiconductor Engineering .

Igniting scalable AMBA-compliant system connectivity. The post From Standards To Systems: The Chiplet Era On Arm appeared first on Semiconductor Engineering .

Complex chips need coherent and non-coherent sub-NoCs to ensure efficient data paths. Correct hierarchy is essential. The post NoC Coherency Challenges Balloon With AI SoCs And Chiplets appeared first on Semiconductor Engineering .

A new technical paper, “Highly energy-efficient manifold microchannel for cooling electronics with a coefficient of performance over 100,000,” was published by researchers at KAIST. The study presents a CMOS-compatible manifold microchannel cooler that removes over 2,000 W/cm² using single-phase water at only 8 kPa pressure drop, achieving a record COP of 106,000—a significant improvement over...…

Security coverage is a key component of a systematic framework for comprehensive, traceable security verification. The post Assuring Comprehensive Security Coverage In Hardware Design appeared first on Semiconductor Engineering .

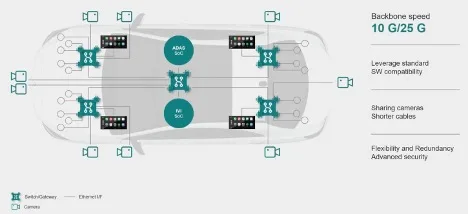

New in-vehicle networking technology will likely take over as more AI is added, but in the near term designers face challenges integrating new with old. The post How Long Will CAN Stick Around As Rival Networks Speed Up? appeared first on Semiconductor Engineering .

Interface IP in 3D; SOCAMM in data centers; edge intelligence implementations; deposition, etch for 3D; interconnect telemetry; design–manufacturing collaboration. The post Blog Review: Apr. 29 appeared first on Semiconductor Engineering .

Transform fragmented, siloed data into a governed, connected, and reusable organizational knowledge base. The post From Silos to Systems, from Data to Insight appeared first on Semiconductor Engineering .

research.io

research.ioSign up to keep scrolling

Create your feed subscriptions, save articles, keep scrolling.